This document describes mechanical and electrical interfaces between the components of a V0 iteration of an HGCROC3-based HRPPD readout backplane. The backplane will consist of a 1024-channel ASIC board (HRPPD\_ASIC\_BOARD.V0), a pair of identical FPGA boards (HRPPD\_FPGA\_BOARD.V0), each serving one half (512 channels) of the ASIC board, and a complementary passive interface between the ASIC board and a KCU105 toolkit (HRPPD\_FMC\_BOARD.V0).

# 1. HRPPD photosensors by Incom Inc.

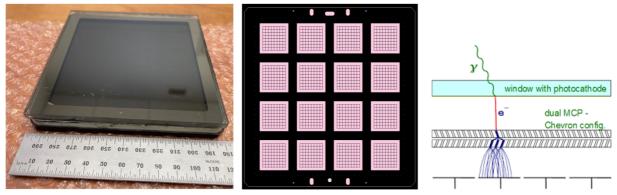

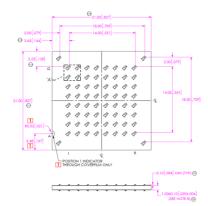

High Rate Picosecond PhotoDetector (HRPPD) by Incom Inc. is a Micro-Channel Plate (MCP) vacuum photosensor of a ~119.6mm x 119.6mm x 14.1mm size (Figure 1, left), with a fused silica window covered by a bialkali photocathode from the inside, ceramic side walls and a ceramic anode base plate, pixelated into 4x4 groups of 8x8 square pads with a pitch of 2.0mm on its outer side (see Figure 1, center), for a total of 1024 channels. Two 600 $\mu$ m thick MCPs

Figure 1 Left: HRPPD photosensor. Center: rear sensor side with sixteen 8x8 pad fields (gerber view). Right: Illustration of HRPPD operation principle.

provide a primary photoelectron amplification via a secondary electron emission off the narrow 10 $\mu$ m diameter channel walls during the "avalanche" development caused by a bias voltage up to ~1kV applied to the top and bottom surfaces of each MCP, see Figure **1** (right) for an illustration.

### 1.1 Mechanical interface to the ASIC board

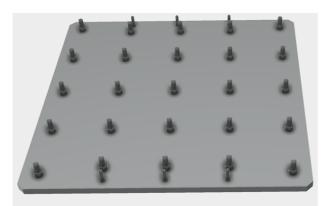

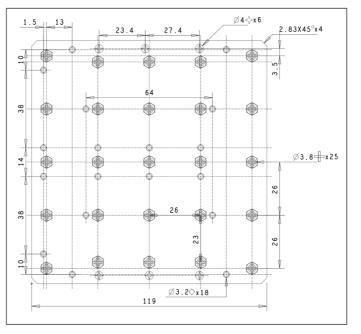

From the mechanical point of view, the pixelated flat rear side of the sensor has six high voltage (HV) pins (<u>https://www.mcmaster.com/95648A280/</u>, STEP <u>model</u>) and 25 socket cap titanium screws (<u>https://www.mcmaster.com/95435A207/</u>, STEP <u>model</u>) with a head diameter of ~3.56mm (0.14"), either glued or brazed in such a way that the heads can be used for the ASIC board alignment with respect to the 2mm pads, and the threaded parts later on used to bolt the ASIC board onto the sensor, see Figure **2**.

Figure 2 HRPPD anode base plate with 25 brazed socket cap screws to mount the ASIC PCB and two groups of three HV pins.

A STEP file with the model of the anode base plate with the pre-mounted HV pins and the cap socket screws is provided <u>here</u>. Be aware that this model is merely a mockup, while the actual *proprietary* (do not share!) Kyocera <u>DXF manufacturing file</u> and a <u>pdf printout</u> describing the High Temperature Co-fired Ceramic (HTCC) stackup of the anode base plate should be used as a primary reference for any dimensions, etc.

groups of three HV pins. A 1.0mm thick 3D printed spacer between the HRPPD ceramic rear side and the ASIC PCB is described in section 1.3.

### 1.2 Single photoelectron pulse shape

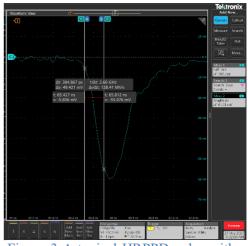

The HRPPD is a so-called DC-coupled device, where charge is directly collected by small square pads with a pitch of 3.25mm on the inner (vacuum) side of the anode base plate. Anode in our setup is the ground level, while the photocathode is typically operated at a negative voltage up to ~2.5kV. Contrary to devices like AC-LGADs, the HRPPD gain *can be varied* during operation by changing the MCP bias voltage, and can comfortably reach few times  $10^6$ , although a preferred setting in the experiment is perhaps few times  $10^5$ . Single photon pulse height can reach dozens of mV (on a 50 Ohm load; depending on the gain). Pulses have leading edge <500ps (as measured from ~20% to ~80% peak value) and duration of 2-3ns, see Figure **3**.

Figure 3 A typical HRPPD pulse with a leading edge ~400ps. Screenshot taken with an 8GHz ABW scope.

### 1.3 Electrical interface to the ASIC board

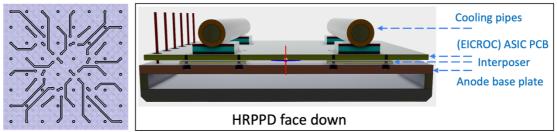

The 104mm x 104mm active area is organized as a uniform 32 x 32 3.00mm square pad field on the inner (vacuum) side of the anode plate (pitch 3.25mm). This ceramic plate not only encloses the vacuum volume but plays the role of a pre-routing PCB with a simple stack up (see Figure 4, left), which provides an electrical connection from the uniform inner pad field to the sixteen groups of 8x8 pads with a smaller pitch on the outer side (see Figure 1, center), in order to simplify interfacing to the ASIC PCB and provide space for the mechanical integration.

Each 8x8 pad field is surrounded by a ~2mm wide ground "band", electrically connected to the internal ground of the ceramic stack-up (as well as to the HV ground pad), see Figure 1 (center).

Figure 4 Left: ceramic stackup routing snapshot between 8x8 3.25mm pitch inner pads and 2.00mm pitch outer side pads (only half of the traces shown). Right: Samtec compression interposer squeezed between the sensor anode plate and the ASIC PCB (*ignore everything above the ASIC PCB in this picture*).

The electrical connection between the HRPPD sensor pads (and the internal ground) and the ASIC board is provided via custom 21mm x 21mm x 1mm size double-sided Samtec ZA1 compression interposers (model ZSP-232827-01-ZA1-D, see also Figure **5**), sandwiched between the sensor and the ASIC board during the assembly procedure, as shown in Figure **4** (right). The interposers are aligned with respect to the HRPPD base plate using 1.0mm thick 3D printed spacers with 25 3.80mm diameter holes matching the screw pattern on the sensor base plate, and a pattern of 4x4 large 21.25mm square openings matching the interposer size.

Figure 5 A custom Samtec compression interposer used with the EIC HRPPDs. Four spring pads in the corners provide a ground connection.

Traces of the internal stackup can be as long as ~10mm (see Figure **4** left, the area here is 26mm x 26mm), implemented in a 50 Ohm coplanar waveguide configuration, and have an estimated capacitance of up to ~2pF/cm (yet to be measured once Kyocera delivers the plates). Pad capacitance to ground is expected to be small. This iteration of the base plate is (somewhat unexpectedly) performed using a so-called High Temperature Co-fired Ceramic (HTCC) technology, therefore the traces are made out of a tungsten alloy rather than copper expected in a Low Temperature (LTCC) case. Since the trace cross-section is small (around 90µm x 10µm), the traces themselves will have a resistivity of up to ~1 Ohm/cm. Molybdenum alloy vias will probably add ~0.15 Ohm to this estimate. Therefore, one can expect that the resistivity of the charge flow path between the

charge collecting pads and the Samtec interposer springs will vary from pad to pad between ~0.2 Ohm and ~1.5 Ohm (will be measured directly end of November 2023 once the plates are delivered to Incom). The full trace capacitance will also vary from pad to pad but should not exceed 2-3pF overall. We have no idea about the Samtec interposer contribution (will be measured directly once we have all components to assemble the whole stack).

Design drawing of the Samtec compression interposer is uploaded <u>here</u>, as well as a <u>STEP</u> <u>model</u>. A <u>STEP model</u> of a 3D printed spacer between the sensor anode plate and the ASIC board is available as well. Need to add recesses for ASIC board studs.

## 2. ASIC board HRPPD\_ASIC\_BOARD.V0

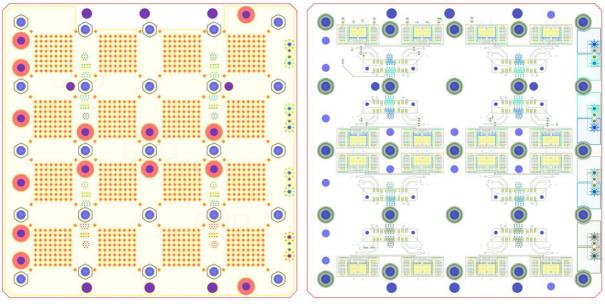

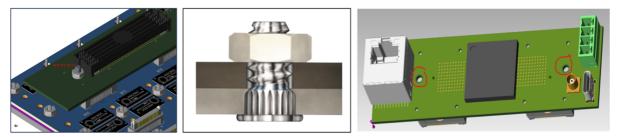

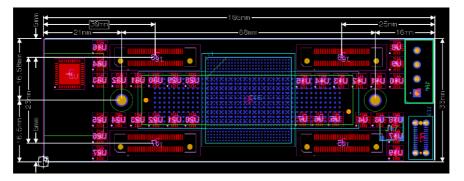

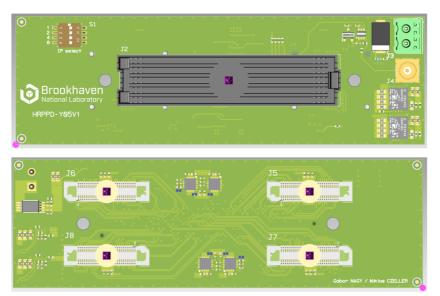

The 1.6mm thick ASIC board has a size of 119mm x 119mm with tapered corners, see the floor plan in Figure **6**. The board hosts sixteen HGCROC3 chips. Each of the ASICs serves a single 8x8 pixels spot, for a total of 64 channels. A current CAD model is uploaded <u>here</u>.

Figure 6 HRPPD\_ASIC\_BOARD\_V0 layout. Left: bottom (HRPPD) side. Right: top (ASIC) side.

#### 2.1 Mechanical and electrical interface to the HRPPD sensor

The ASIC board is bolted onto the HRPPD rear side (anode plate) by 25 socket cap screws, see section 1.1. As seen in Figure 6 (left), the board should therefore have respective 3.80mm diameter through holes (shown in blue) matching the location of the screws on the sensor rear side, and also six 4.00mm diameter holes (shown in purple) in order to not interfere with the sensor high voltage pins. See the CAD model and Figure 7 for the exact locations. A stay clear area around the screw caps on the top side of the ASIC board should be 7.0mm, at a minimum. As described in section 1.3, the HRPPD pads are routed to the bottom side of the ASIC readout board via

Figure 7 ASIC board mechanical hole pattern.

double sided Samtec compression interposers. The ASIC board should therefore have a matching pattern of 1024 spots on its bottom side, as well as the four ground spots per each of the 4x4 64-pad groups, see Figure **6** (left). A bare board CAD model is uploaded here.

### 2.2 Mechanical and electrical interface to the FPGA boards

Control of the ASIC boards will be done via a pair of independent and identical mezzanine FPGA boards described in section 3. Each of the two FPGA boards will serve eight HGCROC3 chips as shown in Figure **8**.

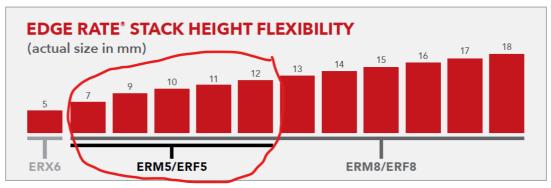

We will use matching 2x30pin Samtec ERM5 (male: <u>ERM5-030-05.0-L-DV-TR</u>, <u>STEP file</u>) and ERF5 (female: <u>ERF5-030-05.0-L-DV-K-TR</u>, <u>STEP file</u>) board-to-board connectors between the ASIC board and the FPGA board. The ERM5 (male) ones will be used on the ASIC board. See the <u>CAD model</u> for exact locations. Every two HGCROC3 ASICs will share one ERM5 connector (see Figure **6**, right). No trigger lines will be used between ASICs and FPGA boards.

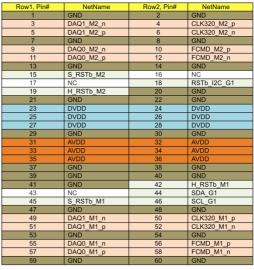

Pin 1 location is shown here. Pin designation is shown in Figure **10**. We will use 1 CLK and 1 FCMD line per ASIC. The I2C bus will be common for every two chips. ASIC chips

Figure 8 One of the two FPGA boards mounted on top of the ASIC board.

served by the same FPGA will have identifiers in a range from 0 to 7 as shown here.

FPGA boards will be snapped onto the ASIC board and mechanically aligned with respect to it by means of the ERM(F)5 connectors. Besides this, each of the FPGA boards will be fixed in situ by a pair of <u>PEM KFH broaching studs</u> (see p.12), which will be pre-mounted onto the ASIC board in a way shown in Figure **9** (center) (requires a 3.00<sup>+0.08</sup>mm diameter hole, see the above document). We assume a 18mm long KFH-M3-18ET stud model will be used, with standard hexagonal M3 nuts (Ø6mm clearance on the top side of FPGA board required, see Figure **9** right). Holes in the FPGA board should match the M3 thread diameter.

Figure 9 Left: FMC board fixed in situ by KFH studs. One can also see three HV pins on top of the picture and a pair of HRPPD screws on the left. Center: PEM KFH broaching stud (here shown in a configuration without a gap between the two boards). Right: locations of the mechanical holes for broaching studs in an FPGA board are indicated in red.

Low voltage power distribution to the ASIC boards will be provided in two different ways:

- FPGA boards will have an LV connector (see Figure 9, right) and a set of DC-DC convertors, and will feed both analog and digital power to the ASIC board via a set of designated pins in each Samtec ERF5 connector (see Figure 10);

- The same functionality is foreseen for the "passive" FMC boards, see section 8;

• Besides this, ASIC boards will have their own LV connector, and *power will be taken from this connector if the respective cable is plugged in*

#### 2.3 Mechanical interface to the cooling cold plate

It is expected that each ASIC will dissipate at most 15mW of power per channel. Active air cooling will be provided by aluminum cold plates with fins directly attached to the ASICs via soft gap pads (reference), see section 5. The details of the cooling setup are not fixed yet, but it is agreed upon that (as indicated in Figure 6), the ASIC board should have eight 3.00<sup>+0.08</sup>mm diameter though holes (shown in pink) to attach cooling system cold plates via the same type of KFH broaching studs used to bolt the FPGA boards to the ASIC board, as explained in section 2.2. See a <u>CAD model</u> of the ASIC board for the exact location of these holes.

### 2.4 Trigger signal digitization

Figure 10 Description of the 2x30 pins of the Samtec ERF(M)5 connectors.

For the purposes of cross FPGA board timing synchronization, each group of two ASICs connected by the same Samtec connector to the FPGA (FMC) boards will use a single channel in a range from 64 to 71 in one of the ASICs to digitize a reference timing pulse. This pulse will be derived from a TTL trigger signal fed into an (M)MCX connector on the FPGA board (see section 3), shaped by the FPGA, and propagated to the ASIC board via a designated TRIG\_Gx pin in each of the Samtec ERF5 connectors. The leading edge of this signal (a level drop from +1.2V to 0V) defines timing reference. The width of this signal should be >500ns and be configurable via FPGA I2C interface together with the delay. These signals will be fed into the respective ASIC input via a serial 2pF capacitor.

# 3. FPGA board HRPPD\_FPGA\_BOARD.V0

#### This section is under construction

This board provides an interface between eight HGCROC3 chips of the ASIC board and the data acquisition PC. For the overall board layout see Figure 8. For the mechanical and electrical interface to the ASIC board see section 2.2.

We are going to use a Kintex Ultrascale (<u>XCKU040</u>) FPGA, also in order to be fully compatible firmware-wise with the KCU105 development kit, see section 4.

### 3.1 Required functionality

This board should have an LV connector (5V) and provide an optional LV power to the ASIC board via Samtec ERF5 connectors, see also section 2.2.

The only data acquisition mode of interest is a single event triggered mode, where a host DAQ guarantees a proper VETO functionality in its fast logic scheme (no spurious trigger signals before the current event is fully read out).

A host DAQ will feed a TTL trigger signal with a minimal duration of 100ns into a single female MCX connector on this FPGA board. Leading edge of this signal defines the FCMD timing. The FPGA board will also feed a derived signal of a standard yet to be defined to the ASIC board for the purposes of timing synchronization, see section 2.4.

The board should provide both USB3.1 and 1Gb ethernet connectivity (~950Mb/s with Jumbo frames, Ethernet PHY:<u>KSZ9131RNX</u>) to the host PC, with the following minimal functionality:

- HGCROC3 ASIC configuration via I2C

- Generation of a configurable L1A FCMD via a software command

- Generation of a configurable L1A FCMD upon receipt of a hardware trigger signal

- A single event data transfer to the host PC

Format of the event record is yet to be defined.

FPGA board should have a header to power up the cooling system fan.

3.2 Layout and a mechanical interface to the cooling cold plate

It is anticipated that the FPGA control board can fit into 105mm x 33mm, see Figure **11**, and have thickness of **1.6mm**.

Figure 11 Layout of the HRPPD\_FPGA\_BOARD.V0. Need a new picture.

All connections (LV, USB, Ethernet, MCX) will be vertical, to simplify HRPPD tiling with a minimal interference between the neighboring sensors.

Cooling interface is yet to be defined (and will require more 3mm diameter through holes).

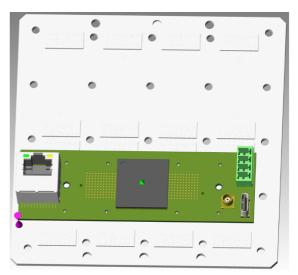

## 4. Passive interface board HRPPD\_FMC\_BOARD.V0

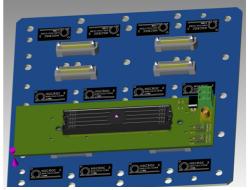

As a backup and a test plan option, we will build a "simple board" which replaces the FPGA board and provides a standard VITA57/FMC connection (<u>ASP\_134603\_01</u>), which allows us to use a KCU105 development kit for first tests of the ASIC board. This board should be mechanically compatible with the FPGA board HRPPD\_FPGA\_BOARD.V0 in terms of:

- dimensions

- location of the Samtec ERF5 connectors

- location of the two mounting through holes for the KFH studs

We are going to use a standard Samtec FMC cable (HDR-169470-01) to provide connectivity to a KCU105 development kit, see Figure **12**.

It is expected that this board will be typically used in a configuration with only a few powered up ASIC chips. Therefore, no cooling fan will be used, and as such no mechanical compatibility between the Twinax cable and the cooling system fan is required.

This board should provide LV to the ASIC board, in the same way the FPGA board does. It will distribute the trigger signal via an onboard female MCX connector the same way the FPGA board does. Pinout of the FMC connector, of the four Samtec connectors, as well as the schematics of the trigger input is provided <u>here</u>. Stackup, component placement and critical dimensions are <u>available</u> as well. STEP file is provided <u>here</u>. See also Figure **13**, and images of the top and bottom sides in Figure **14**.

Figure 12 Samtec cable to provide connectivity between a HRPPD\_FMC\_BOARD.V0 board and a KCU105 kit.

Figure 13 HRPPD\_ASIC\_BOARD\_V0 with one HRPPD\_FMC\_BOARD.V0 mounted.

Figure 14 HRPPD FMC BOARD.V0 board (top and bottom sides).

# 5. Cooling system setup

Air cooling will be realized by installing a set of three separate aluminum cold plates with fins, which will be directly attached to the ASICs, FPGAs and other power dissipating components, presumably via appropriate soft pads. Mechanical connection to either the ASIC board or FPGA boards will be made by KFH broaching studs (eight for the ASIC board heat sink and two for each of the FPGA boards), see also section 2.2. A single 92mm diameter fan will be used for each HRPPD sensor assembly consisting of a sensor itself, an ASIC board and a pair of FPGA boards.

Figure 16 A tentative cooling system setup, shown with a fan masked out (FMC board configuration).

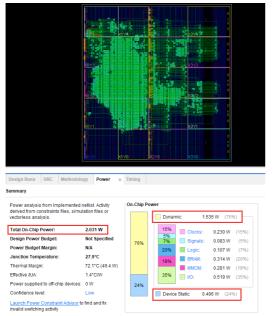

A full power budget of such an assembly is expected to be ~??W, with <1.2W per ASIC, <2.3W per each of the two FPGAs assuming a 10% margin (see Figure **15**), and <??W for all other active components. A preliminary CAD model is shown in Figure **16**.

The details of this system will be defined once the mechanical layout of the ASIC and FPGA boards is decided, and in particular the height of the ERF(M)5 connectors is agreed upon, as defined by the size of the active components (2..4mm height expected).

## 6. Appendix

|                                       | Parameter               | Comments                         |

|---------------------------------------|-------------------------|----------------------------------|

| FPGA-ASIC board interface             |                         |                                  |

| Differential signal standard          | DIFF_SSTL12_DCI         |                                  |

| LVDS<->CLPS level convertors          | none                    |                                  |

| Termination of the CLK and FCMD lines | Done on the ASIC board  |                                  |

| Termination of the DATA lines         | Done inside of the FPGA | No additional resistors required |

| DAQ signal interface          | MCX female                                            |                                     |

|-------------------------------|-------------------------------------------------------|-------------------------------------|

| Trigger signal (FPGA boards)  | TTL, 100ns minimum, leading<br>edge from ~0V to +2.5V |                                     |

| Timing reference (ASIC board) | 500ns minimum, leading edge<br>from +1.2V to 0V       | Derived from the trigger TTL signal |

# 7. Spares

(if needed the EFR5/ERM5 connectors has a different height option up to 12mm)

It's important to do a real BOM list with all PCB, connectors and mechanical parts needed. Actually, my board is called 2310\_Hrppd\_Asic\_Board and Y05 for Alexander card.