eic-projdet-pfrich-electronics-l AT lists.bnl.gov

Subject: ePIC pfRICH electronics mailing list

List archive

Re: [Eic-projdet-pfrich-electronics-l] First draft of the FPGA board layout

- From: "Kiselev, Alexander" <ayk AT bnl.gov>

- To: nagy g <hunagabo AT gmail.com>

- Cc: Pierrick Dinaucourt <pdinaucourt AT omega.in2p3.fr>, "Cacace, Daniel" <dcacace AT bnl.gov>, Czeller Miklos <czeller.miklos AT gmail.com>, "novitzkyn AT ornl.gov" <novitzkyn AT ornl.gov>, "Camarda, Timothy via Eic-projdet-pfrich-electronics-l" <eic-projdet-pfrich-electronics-l AT lists.bnl.gov>

- Subject: Re: [Eic-projdet-pfrich-electronics-l] First draft of the FPGA board layout

- Date: Fri, 29 Sep 2023 03:51:57 +0000

Hi Gabor, All,

(Cc to the whole list)

In this discussion I cannot give much of the answers, but rather help you experts come to definitive decisions. So mostly I'm going to ask questions, pick up on proposals, and keep track on all of the valid items so that we do not forget too many of them.

Should I probably set up a google doc "dashboard" Web page, or otherwise do we have means to leave comments in a shared Word document concurrently?

Concerning the screws, can we preliminary agree on something like KFH broaching studs in a brochure you shared last time:

https://www.mouser.com/datasheet/2/974/kdata-1901229.pdf ? 18mm length should be enough. They will certainly fit into the ASIC board if placed between the 21mm x 21mm interposer footprints

(Gabor: I'd say this is a hard requirement for any solution, since otherwise routing of the ASIC board will quickly become a nightmare; please check location of these holes in your present layout).

Otherwise we should just define the location and the diameter of a stay clear zone for the ASIC board now. Naively I'd say we better avoid anything which is either glued or mounted onto the ASIC PCB from its top side, since the force when tightening the

nut will in our use case be pulling the stud out of the PCB.

Miklos, we will certainly make use of extra channels (at least one for each group of clock-synchronized ASICs), so a 64-channel mode of operation is kind of excluded.

Pierrick, anything presented / discussed so far causes an immediate concern?

Cheers,

Alexander.

From: nagy g <hunagabo AT gmail.com>

Sent: Thursday, September 28, 2023 12:03 PM

To: Kiselev, Alexander <ayk AT bnl.gov>

Cc: Pierrick Dinaucourt <pdinaucourt AT omega.in2p3.fr>; Cacace, Daniel <dcacace AT bnl.gov>; Czeller Miklos <czeller.miklos AT gmail.com>; novitzkyn AT ornl.gov <novitzkyn AT ornl.gov>

Subject: Re: First draft of the FPGA board layout

Sent: Thursday, September 28, 2023 12:03 PM

To: Kiselev, Alexander <ayk AT bnl.gov>

Cc: Pierrick Dinaucourt <pdinaucourt AT omega.in2p3.fr>; Cacace, Daniel <dcacace AT bnl.gov>; Czeller Miklos <czeller.miklos AT gmail.com>; novitzkyn AT ornl.gov <novitzkyn AT ornl.gov>

Subject: Re: First draft of the FPGA board layout

HI Alexander,

No, nothing against sharing this mailing thread with anyone. Please do it if it useful.

For the easier following of the answers I copy your questions here with grey backgrounded italic text.

e-mail text: I recall Christophe suggested that power to the ASIC board will not be provided

via FPGA board, at least in V0. In practice this means that it can be beneficial to shorten the FPGA board by ~5mm or so on the USB connector end, to have enough space for a vertically mounted power connectors (and cables!) of the ASIC board. Also may be useful

to reserve this space for (M)MCX connectors for triggering (if they will be located on the ASIC board) and synchro-pulses (to be fed into one of the channels 64..71 of either each ASIC or each group of clock-synchronized ASICs)

That is fine, but for future use, I would keep that pins assigned to powering the ASICs.

Are there any issues with providing power to the ASIC and FPGA boards from separate power supplies? Ground connection

between the two boards is done via ERF(M)5 connectors. Is it the power supply ground as well?

For the test it can work, but I would avoid grounding loops as much as possible in a noisy environment. Mostly if we have a changing magnetic field around

the system.

To be honest I would prefer to use a 4 pin connector in the later systems, and even the ASIC power is coming from outside, that could go via the FPGA board. In that

case the Ground (and the noise) could be more controlled.

p.1: if this is the ASIC board view rather than a spacer with Samtec interposers, then this drawing needs to

be updated (ASIC locations are not current); if it is a spacer+interposers, then ASICs need to be removed

I will update it.

p.2: all fine with me, but bear in mind that we are almost certainly not going to use these uni-directional trigger lines

for any practical purposes. If no one is going to play streaming readout games with this hardware, we can probably decide ditching these lines (and use connectors with a smaller pin count, which is also good to minimize the insertion / removal force). Miklos

and Norbert: please comment.

As far as I understand at least two trigger line (2x2, because of differential signaling) needed, but if that is not true, let me know.

If those are not needed, then we can use a 2x20 pin connectors

p.3: all fine with me. We definitely need a USB interface, to start with. Do we need a separate JTAG header? And perhaps

a separate UART header a la KCU105?

JTAG is definitely needed, but that is only for debugging, so I did not show that now. (but to make our life easier, we need to use the standard Xilinx

2x7 pin 2mm header)

I do not think UART is needed separately, but it is fine to place a small connector for it or a test points...

p.4: all fine with me

p.5: I tend to agree we may not need standoffs. But there should be nuts embedded into the ASIC board, correct?

If we have a press-fit nuts, then we should screw from the bottom side, so I am not sure what we need... it depends what you can add to the ASIC board.

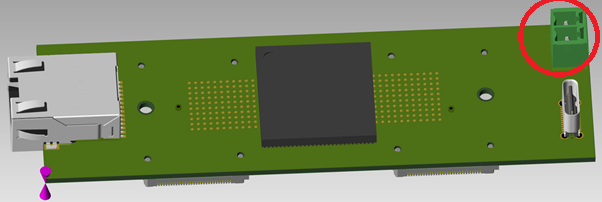

The most simple solution, if screws can be attached to the ceramic or ASIC board and the FPGA board has only a hole for those screws. Like the one on the picture:

The distance between the ASIC and FPGA board will be defined anyway by the connectors, so we just need to guarantee, the two boards will stay in position.

But I am also fine to add nuts..

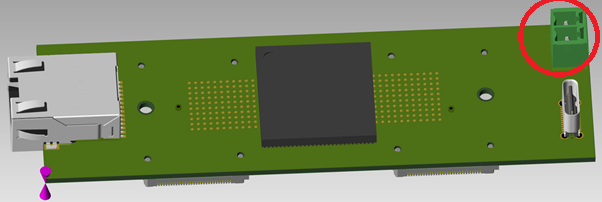

p.6: Can you think of placing FPGA on the bottom side of the board?

As far as I see now, it can work to move the FPGA to the bottom side, and probably will help in cooling as well. (if we have a metal plate between the

ASIC and FPGA boards. The machined one piece heat-sink I mean.)

Br, gabor

Kiselev, Alexander <ayk AT bnl.gov> ezt írta (időpont: 2023. szept. 28., Cs, 6:46):

Thank you Gabor,

I think this is a pretty good first iteration. Anything against forwarding this e-mail (and the subsequent exchange) to the whole list (eic-projdet-pfrich-electronics-l AT lists.bnl.gov)?

Daniel, Pierrick: please provide your feedback, especially on the integration.

My feedback, following the discussion we had last Friday:

e-mail text: I recall Christophe suggested that power to the ASIC board will not be provided via FPGA board, at least in V0. In practice this means that it can be beneficial to shorten the FPGA board by ~5mm or so on the USB connector end, to have enough space for a vertically mounted power connectors (and cables!) of the ASIC board. Also may be useful to reserve this space for (M)MCX connectors for triggering (if they will be located on the ASIC board) and synchro-pulses (to be fed into one of the channels 64..71 of either each ASIC or each group of clock-synchronized ASICs)

Are there any issues with providing power to the ASIC and FPGA boards from separate power supplies? Ground connection between the two boards is done via ERF(M)5 connectors. Is it the power supply ground as well?

p.1: if this is the ASIC board view rather than a spacer with Samtec interposers, then this drawing needs to be updated (ASIC locations are not current); if it is a spacer+interposers, then ASICs need to be removed

p.2: all fine with me, but bear in mind that we are almost certainly not going to use these uni-directional trigger lines for any practical purposes. If no one is going to play streaming readout games with this hardware, we can probably decide ditching these lines (and use connectors with a smaller pin count, which is also good to minimize the insertion / removal force). Miklos and Norbert: please comment.

p.3: all fine with me. We definitely need a USB interface, to start with. Do we need a separate JTAG header? And perhaps a separate UART header a la KCU105?

p.4: all fine with me

p.5: I tend to agree we may not need standoffs. But there should be nuts embedded into the ASIC board, correct?

p.6: Can you think of placing FPGA on the bottom side of the board?

Was there any other circuitry on the present carrier board, which may be useful to have on this FPGA board?

I understand that (1) ERF(M)5 connector height does not affect anything in the design, but the details of the cooling system, and can be decided later, (2) nuts or posts to mount the cooling system will be a headache for Pierrick, and do not affect the design of the FPGA board, as long as it stays within its agreed upon footprint, correct? Actually there is not much space on the ASIC board to embed these nuts. Daniel: how many do we actually need?

Cheers,Alexander.

From: nagy g <hunagabo AT gmail.com>

Sent: Wednesday, September 27, 2023 4:38 PM

To: Kiselev, Alexander <ayk AT bnl.gov>

Cc: Pierrick Dinaucourt <pdinaucourt AT omega.in2p3.fr>; Cacace, Daniel <dcacace AT bnl.gov>; Czeller Miklos <czeller.miklos AT gmail.com>

Subject: Re: First draft of the FPGA board layoutHi All,

I give it up for today, so please find attached the current version of the FPGA board document.

NOTES:- Ethernet connector has not changed to a vertical one yet- The FMC connector has put on the same board, to do not maintain two models until the conception is not finished- The power to the ASICs will be provided via the ERF5/ERM5 connectors, but at the moment I am not sure we can denerate it onboard- So, in the worst case we can change the power connector to the 4 pin version and generate the 1.2V externally...- HV voltage is not goind through the FMC or FPGA card, but goes directly to the ASICs board

Br, gabor

nagy g <hunagabo AT gmail.com> ezt írta (időpont: 2023. szept. 27., Sze, 19:49):

Hi Alexander,

Our plan is that, in parallel with my PCB design work, Miklos will work on the VHDL code, and pin assignments and other issues (time domains, clock distribution, timing/tuning issues...) can be found even during PCB design time.So, I do not expect a major issues after V0 has finished if the concept what we put together now is good enough... I mean yes, during the V1 debug time, fixes on the PCB can happen in parallel.(((But I try to be conservative as much as possible, because it is always suspicous if something looks too "easy".)))

At the moment the hardes part seems to be the power supplies, especially the correct placement and heat distribution in this limited space, but I had not enough time to see details yet.

Br, gabor

Kiselev, Alexander <ayk AT bnl.gov> ezt írta (időpont: 2023. szept. 27., Sze, 19:07):

Hi Gabor,

Sounds good! Concerning our over-optimistic milestones, I actually start thinking that we need to pack two iterations of the design (V1 & V2) in the period of January-May 2024. Essentially the V1 can have early bug fixes of V0 implemented, and be designed and ordered in parallel with the V0 debugging / evaluation. If it comes out ok, we are good. Otherwise, there will still be some time to order V2. I do not care about money at this point. It's all about being on time.

A question I have to both Pierrick and Gabor is: do I get it right that once the layout of V0 is done, we expect only minor modifications to the design of V1 (and V2?) boards? I mean do we really need several weeks of re-design in 2024, or this work can happen in parallel with a previous version evaluation?

Cheers,Alexander.

From: nagy g <hunagabo AT gmail.com>

Sent: Wednesday, September 27, 2023 10:16 AM

To: Kiselev, Alexander <ayk AT bnl.gov>

Cc: Pierrick Dinaucourt <pdinaucourt AT omega.in2p3.fr>; Cacace, Daniel <dcacace AT bnl.gov>

Subject: Re: First draft of the FPGA board layoutHi Alexander,

I am working on that, but I could not reach the state to provide valuable information. But I will send out a new document today. I promisse :)Br, gabor

Kiselev, Alexander <ayk AT bnl.gov> ezt írta (időpont: 2023. szept. 27., Sze, 15:05):

Hello Gabor,

Do you think you can already share a first approximation of this board with Pierrick and Daniel? The earlier we start substantial iterations the better. Once the interface is fixed (hopefully by the end of next week), everyone can start working in parallel.

Cheers,Alexander.

- Re: [Eic-projdet-pfrich-electronics-l] First draft of the FPGA board layout, Kiselev, Alexander, 09/28/2023

Archive powered by MHonArc 2.6.24.