eic-projdet-pfrich-electronics-l AT lists.bnl.gov

Subject: ePIC pfRICH electronics mailing list

List archive

Re: [Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0

- From: "Pat Bailey" <patrick.bailey AT palpilot.com>

- To: "'nagy g'" <hunagabo AT gmail.com>

- Cc: <Fred.Pascucci AT palpilot.com>, <Cindy.ho AT palpilot.com>, <vicky.sun AT palpilot.com.cn>, "'Camarda, Timothy via Eic-projdet-pfrich-electronics-l'" <eic-projdet-pfrich-electronics-l AT lists.bnl.gov>, "'Alexander'" <ayk AT bnl.gov>, "'Timothy'" <tcamarda AT bnl.gov>

- Subject: Re: [Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0

- Date: Wed, 29 Nov 2023 14:13:58 -0600

Hi Gabor,

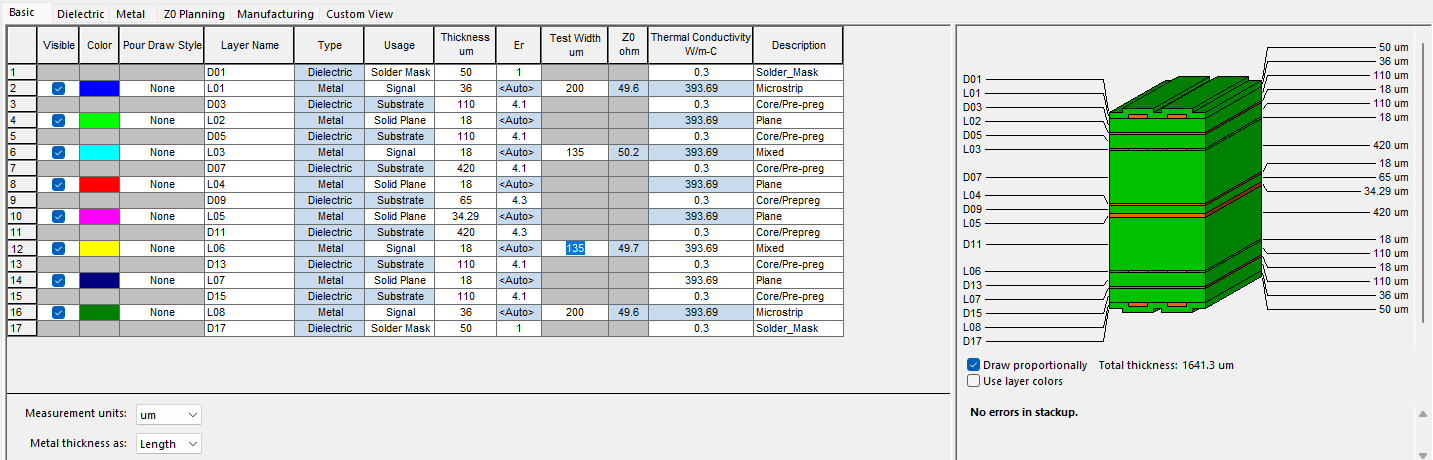

You can use metric and 100um/250um is fine.

Thank you.

Regards,

Pat Bailey Senior Field Application Engineer

Tel: 507 640-0339 patrick.bailey AT palpilot.com

From: nagy g <hunagabo AT gmail.com>

Thank you Pat! I changed the L5 to 0.5oz, which was a mistake.

Yes, the overal thickness is palned to be ~62mil on this board too.

I do design in mm and 4/10mil for laser vis can be 100um/250um, or should be axactly 4/10mil? (just to make sure after conversion it will not cause an error...)

Thanks, gabor

Pat Bailey <patrick.bailey AT palpilot.com> ezt írta (időpont: 2023. nov. 29., Sze, 17:03):

|

-

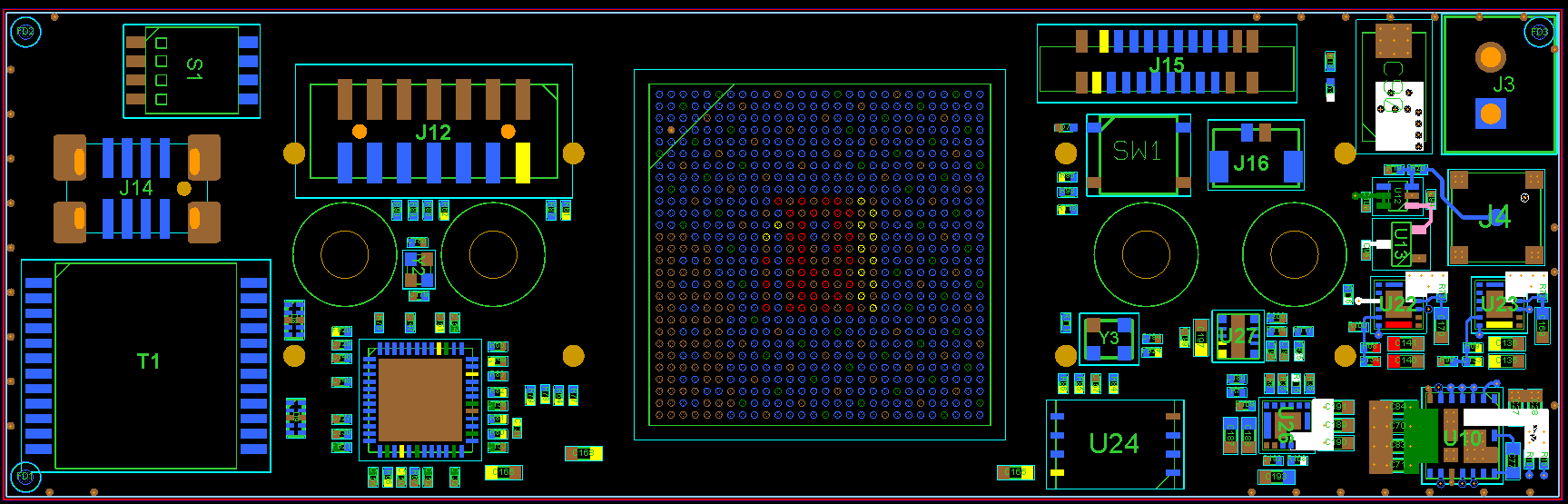

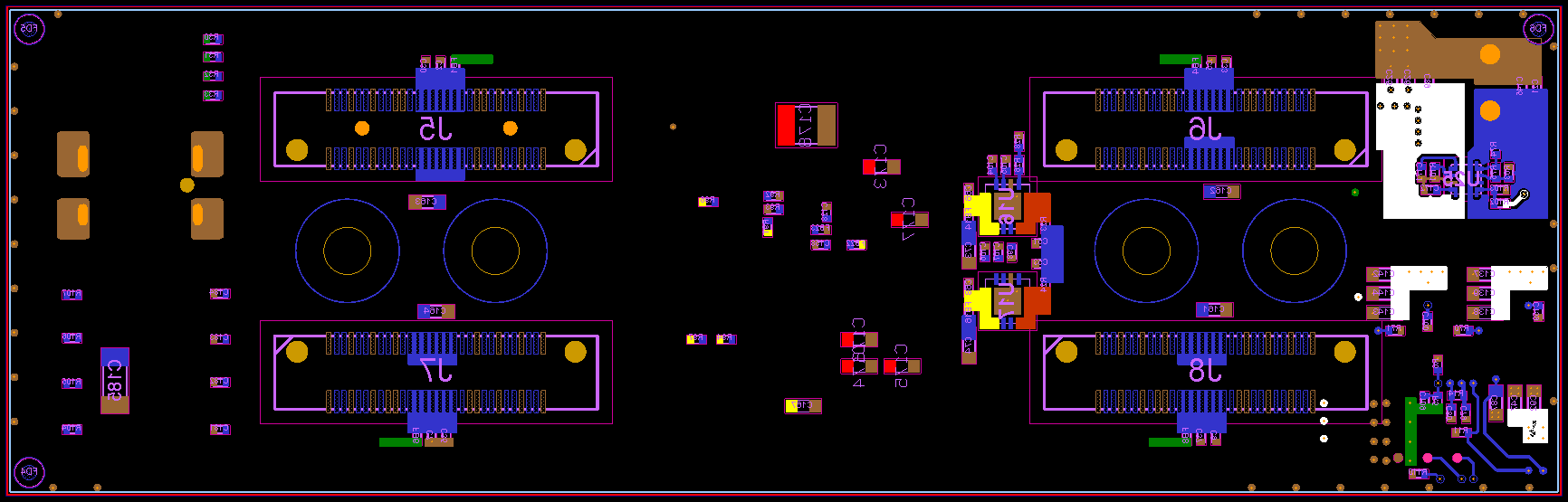

[Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0,

nagy g, 11/29/2023

-

Re: [Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0,

Pat Bailey, 11/29/2023

-

Re: [Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0,

nagy g, 11/29/2023

- Re: [Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0, Pat Bailey, 11/29/2023

- Re: [Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0, Pat Bailey, 11/29/2023

-

Re: [Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0,

nagy g, 11/29/2023

-

Re: [Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0,

Pat Bailey, 11/29/2023

Archive powered by MHonArc 2.6.24.