eic-projdet-pfrich-electronics-l AT lists.bnl.gov

Subject: ePIC pfRICH electronics mailing list

List archive

[Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0

- From: nagy g <hunagabo AT gmail.com>

- To: Patrick Bailey <patrick.bailey AT palpilot.com>, "Fred.Pascucci AT palpilot.com" <Fred.Pascucci AT palpilot.com>, "Cindy.ho AT palpilot.com" <Cindy.ho AT palpilot.com>, "vicky.sun AT palpilot.com.cn" <vicky.sun AT palpilot.com.cn>, "Camarda, Timothy via Eic-projdet-pfrich-electronics-l" <eic-projdet-pfrich-electronics-l AT lists.bnl.gov>, Alexander <ayk AT bnl.gov>, Timothy <tcamarda AT bnl.gov>

- Subject: [Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0

- Date: Wed, 29 Nov 2023 08:21:44 +0100

Hello Fred, Pat, Cyndy and Vicky,

I am working on the nex board in Alexander's project, and would like to get some help in advanced. Just to avoid as much as possible, design chages after routing.

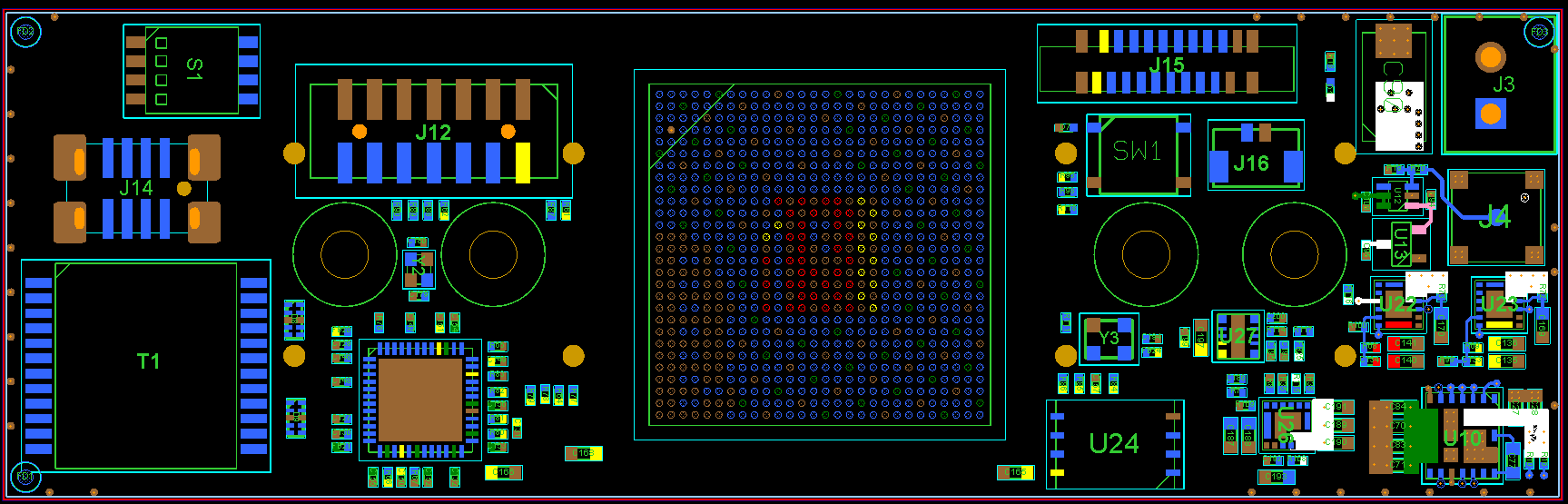

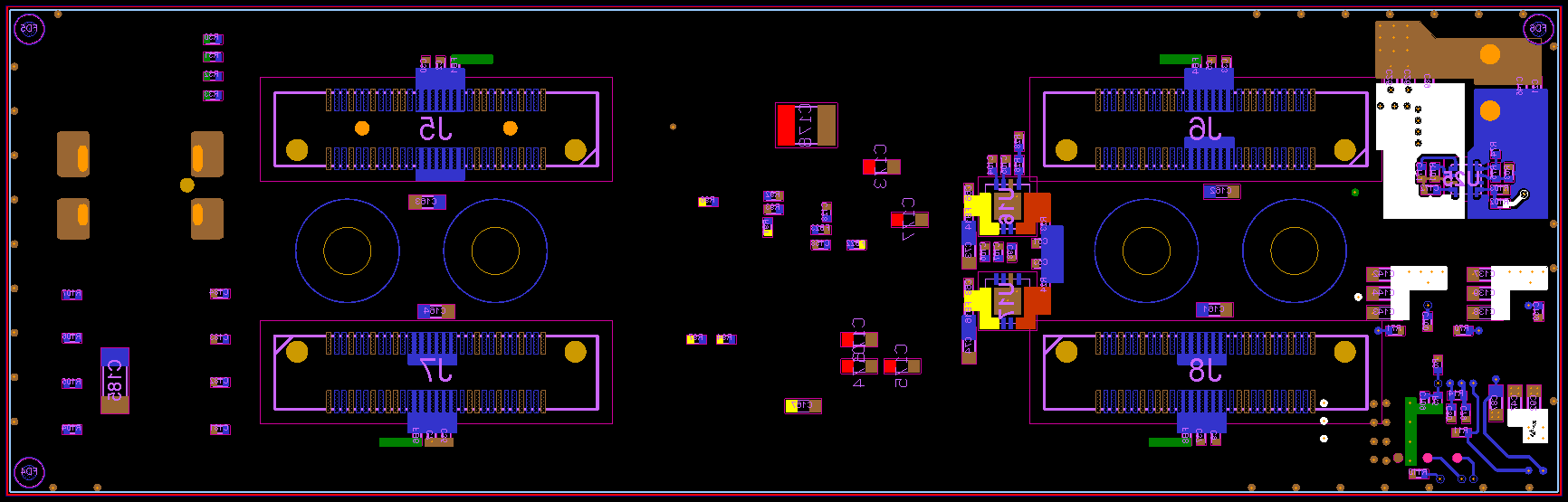

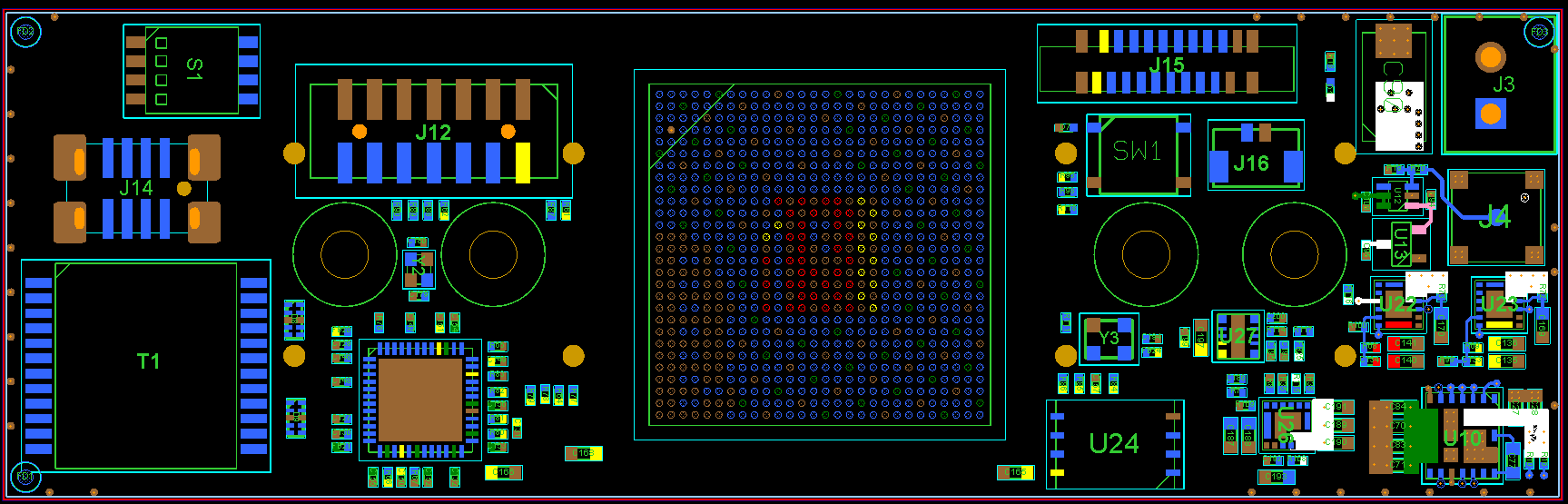

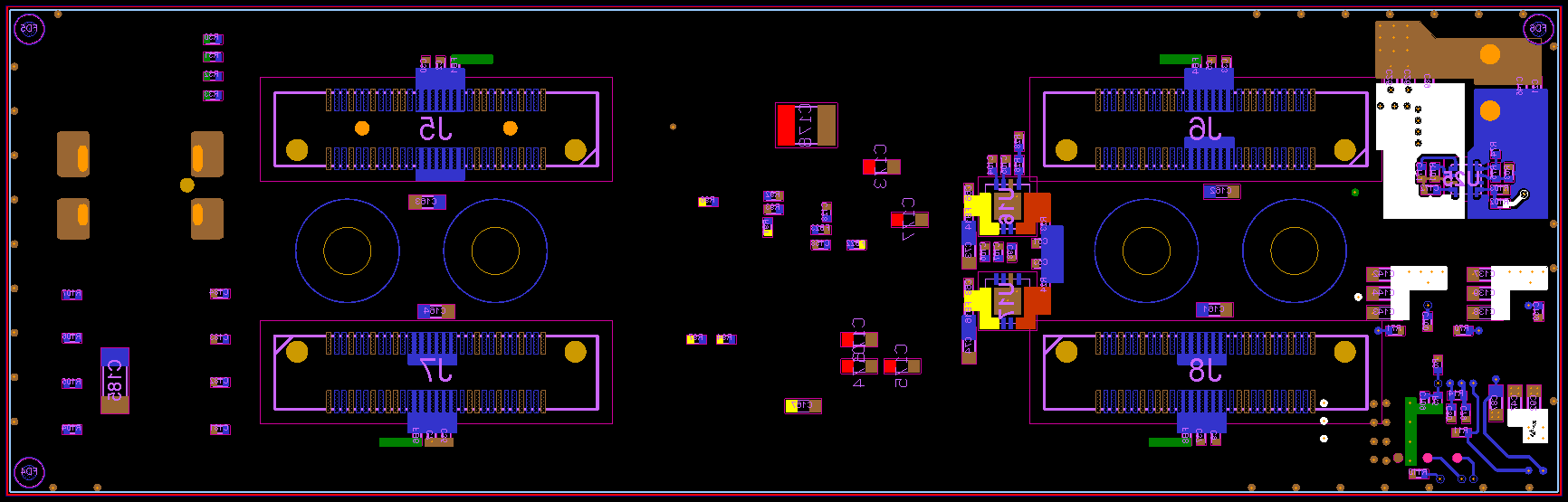

This board is similar in size and shape to the previous one, but more dense in booth side. So probably 8 layer is needed and has a lot of components pad conflicting with the opposit side component.

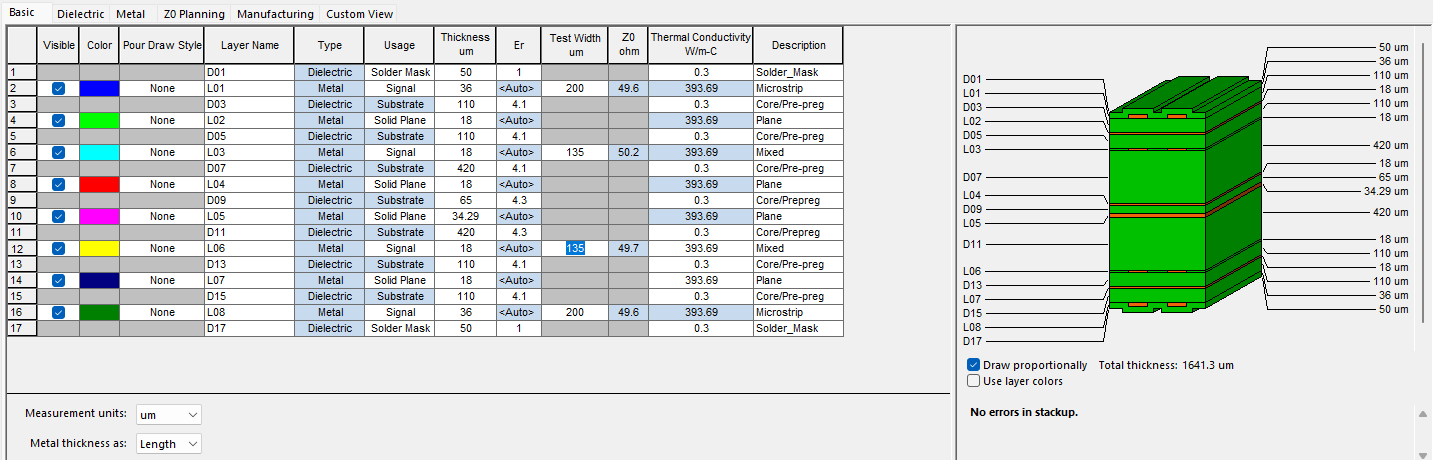

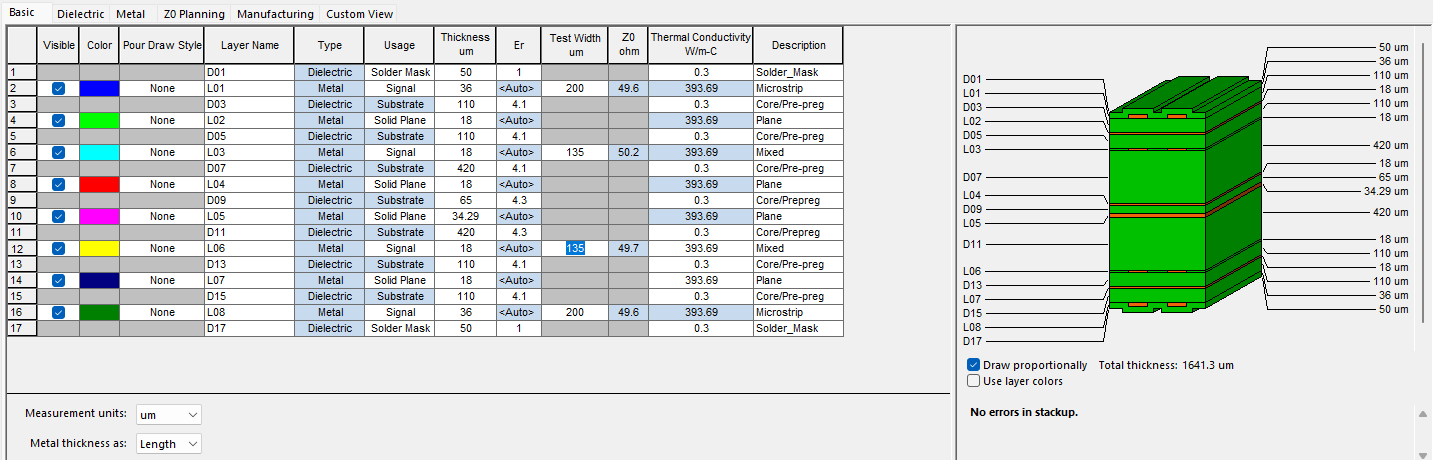

Current plan is to use a HDI 2-4-2 structure (micro VIA 1-2, 1-3, 6-8,7-8 and burried VIA 3-6).

First question would be the stackup. Could you advice what stackup I should use? (need 50Ohm impedance on 1,3,6,7)

I put together something like this (using IT180A):

The next questions would be the uVIA usage.

- Can I use stacked VIAs or staggered VIA is prefered?

- skip VIA is suported or should I avoid? (L1-L3 and L6-L8)

- how much uVIA and through hole VIA can be mixed on same board? (it is recommended to do not mix them in same design in FPGA datasheet, but I have no experience in this.. But would be beneficial to use TH VIA for power supplies.)

This is all for first iteration :)

Thanks, gabor

-

[Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0,

nagy g, 11/29/2023

-

Re: [Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0,

Pat Bailey, 11/29/2023

-

Re: [Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0,

nagy g, 11/29/2023

- Re: [Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0, Pat Bailey, 11/29/2023

- Re: [Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0, Pat Bailey, 11/29/2023

-

Re: [Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0,

nagy g, 11/29/2023

-

Re: [Eic-projdet-pfrich-electronics-l] HRPPD_FPGA_BOARD_V0,

Pat Bailey, 11/29/2023

Archive powered by MHonArc 2.6.24.